-

IP

-

ProcessorsGeon Secure Execution ProcessorSecurityBA20 PipelineZero Embedded ProcessorBA21 Low-Power Embedded ProcessorBA22-DE Deeply Embedded ProcessorBA22-CE Cache Enabled ProcessorBA22-AP Basic Application ProcessorBA25 Advanced Application ProcessorPeripheralsAC97 Audio ControllerSubsystemsDDR2/DDR SDRAM Memory ControllerGeneral Purpose Debug Interface ControllerGPIO ControllerJTAG TAP (Test Access Port) ControllerMAC 10/100/1000 Ethernet ControllerSDRAM/FLASH/SRAM Memory ControllerPCI 32 Bridge ControllerUART 16550 Serial ControllerVGA/LCD Display ControllerEvaluation

-

-

Processors

-

Security

-

Peripherals

-

Development tools

-

Company

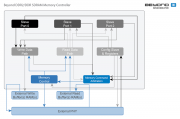

Beyond DDR2/DDR SDRAM Memory Controller

SDRAM memory evolution is going into the direction of increased latency at increased frequency. Beyond DDR2/DDR SDRAM Memory Controller IP Core was developed with this trend in mind. It interleaves accesses from multi-port front-end when possible, maximizing utilization of memory control and data buses. This utilizes higher memory bandwidth capabilities as additional latency cycles can be used for housekeeping operations – bank, row and refresh management.

Controller supports wide variety of applications with its comprehensive set of compile time and run time configuration options. Physical layer (PHY) interface is simple generic interface that can easily connect to various PHY implementations.

| Memory Interface |

|

| Supported SoC Bus Interconnect |

|

| Core Internals |

|

If you would like to inform yourself further about Beyond Semiconductor products, please complete the webform below and let us know your questions, requirements or requests.

Please note that all submitted information will be handled confidentially and used only to address your inquiry. Therefore, we kindly ask you to fill out all the fields of the form.

You may expect our answer shortly.

Copyright © 2006 - 2026 Beyond Semiconductor. All rights reserved.